#### **CODE TIME TECHNOLOGIES**

# mAbassi RTOS

# Porting Document SMP / ARM Cortex-A9 – Xilinx SDK (GCC)

#### **Copyright Information**

This document is copyright Code Time Technologies Inc. ©2013-2018. All rights reserved. No part of this document may be reproduced or distributed in any form by any means, or stored in a database or retrieval system, without the written permission of Code Time Technologies Inc.

Code Time Technologies Inc. may have patents or pending applications covering the subject matter in this document. The furnishing of this document does not give you any license to these patents.

# Disclaimer Code Time Technologies Inc. provides this document "AS IS" without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Code Time Technologies Inc. does not warrant that the contents of this document will meet your requirements or that the document is error-free. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the document. Code Time Technologies Inc. may make improvements and/or changes in the product(s) and/or program(s) described in the document at any time. This document does not imply a commitment by Code Time Technologies Inc. to supply or make generally available the product(s) described herein.

ARM and Cortex are registered trademarks of ARM Limited. Xilinx and Zynq is a registered trademark of Xilinx Inc. Sourcery CodeBench is a registered trademark of Mentor Graphics. All other trademarks are the property of their respective owners.

## **Table of Contents**

| 1  | IN   | FRODUCTION                                                                           | 8    |

|----|------|--------------------------------------------------------------------------------------|------|

|    | 1.1  | DISTRIBUTION CONTENTS                                                                | 8    |

|    | 1.2  | LIMITATIONS                                                                          | 8    |

|    | 1.3  | FEATURES                                                                             | 8    |

| 2  | TA   | RGET SET-UP                                                                          | . 10 |

|    | 2.1  | BUILD OPTIONS (GUI)                                                                  | . 10 |

|    | 2.2  | TARGET DEVICE                                                                        | . 13 |

|    | 2.3  | STACKS SET-UP                                                                        | . 14 |

|    | 2.4  | NUMBER OF CORES                                                                      | . 16 |

|    | 2.5  | PRIVILEGED MODE                                                                      |      |

|    | 2.6  | L1 & L2 CACHE SET-UP                                                                 |      |

|    | 2.7  | SATURATION BIT SET-UP                                                                |      |

|    | 2.8  | SPINLOCK IMPLEMENTATION                                                              |      |

|    | 2.9  | SPURIOUS INTERRUPT                                                                   |      |

|    |      | THUMB2                                                                               |      |

|    |      | VFP / NEON SET-UP                                                                    |      |

|    |      | MULTITHREADING                                                                       |      |

|    |      | PERFORMANCE MONITORING                                                               |      |

|    |      | CODE SOURCERY / YAGARTO                                                              |      |

|    |      |                                                                                      |      |

| 3  | INT  | TERRUPTS                                                                             | . 27 |

|    | 3.1  | INTERRUPT HANDLING                                                                   | 27   |

|    | 3.1  |                                                                                      |      |

|    | 3.1  | 1                                                                                    |      |

|    | 3.2  | FAST INTERRUPTS                                                                      |      |

|    | 3.3  | NESTED INTERRUPTS                                                                    |      |

| 4  | STA  | ACK USAGE                                                                            | . 29 |

| 5  | MF   | EMORY CONFIGURATION                                                                  | . 30 |

| 6  |      | ARCH SET-UP                                                                          |      |

| 7  |      | I                                                                                    |      |

| ,  | Ar.  |                                                                                      |      |

|    | 7.1  | DATAABORT_HANDLER                                                                    |      |

|    | 7.2  | FIQ_HANDLER                                                                          |      |

|    | 7.3  | PFABORT_HANDLER                                                                      |      |

|    | 7.4  | SWI_HANDLER                                                                          |      |

|    | 7.5  | Under_Handler                                                                        | . 37 |

| 8  | CH   | IP SUPPORT                                                                           | . 38 |

|    | 8.1  | GICENABLE                                                                            | . 39 |

|    | 8.2  | GICINIT                                                                              |      |

| 9  | MF   | CASUREMENTS                                                                          | 41   |

|    |      |                                                                                      |      |

|    | 9.1  | MEMORY                                                                               |      |

|    | 9.2  | LATENCY                                                                              | . 43 |

| 10 | Al   | PPENDIX A: BUILD OPTIONS FOR CODE SIZE                                               | . 47 |

|    | 10.1 | CASE 0: MINIMUM BUILD                                                                | . 47 |

|    |      | CASE 1: + RUNTIME SERVICE CREATION / STATIC MEMORY + MULTIPLE TASKS AT SAME PRIORITY |      |

| 12 | 2 R  | EVISION HISTORY                                                        | 56 |

|----|------|------------------------------------------------------------------------|----|

| 1  | 1 R  | EFERENCES                                                              | 55 |

|    |      |                                                                        |    |

|    | 10.8 | CASE 7: FULL BUILD ADDING THE OPTIONAL TIMER SERVICES                  | 54 |

|    | 10.7 | CASE 6: FULL FEATURE BUILD (NO NAMES / NO RUNTIME CREATION)            | 53 |

|    | 10.6 | CASE 5: FULL FEATURE BUILD (NO NAMES)                                  | 52 |

|    |      | CASE 4: + EVENTS / MAILBOXES                                           |    |

|    | 10.4 | CASE 3: + TIMER & TIMEOUT / TIMER CALL BACK / ROUND ROBIN              | 50 |

|    |      | Case 2: + Priority change / Priority inheritance / FCFS / Task suspend |    |

Rev 1.9 Page 4

# **List of Figures**

| FIGURE 2-1: "C" BUILD OPTION SETTING                   | 10 |

|--------------------------------------------------------|----|

| FIGURE 2-2: "ASM" BUILD OPTION SETTING (THROUGH "GCC") | 11 |

| FIGURE 2-3: USING THE ASSEMBLER IN THE GUI             | 12 |

| FIGURE 2-4: "ASM" BUILD OPTION SETTING (THROUGH "AS")  | 13 |

Rev 1.9 Page 5

## **List of Tables**

| Table 1-1 Distribution                                        | 8  |

|---------------------------------------------------------------|----|

| TABLE 2-1 ASSEMBLY BUILD OPTIONS PASSED THROUGH THE COMPILER  |    |

| TABLE 2-2 ASSEMBLY BUILD OPTIONS PASSED THROUGH THE ASSEMBLER | 12 |

| TABLE 2-3 OS_PLATFORM VALID SETTINGS                          |    |

| TABLE 2-4 OS_PLATFORM MODIFICATION                            |    |

| TABLE 2-5 COMMAND LINE SET OF OS_PLATFORM                     |    |

| TABLE 2-6 STACK SIZE TOKENS.                                  |    |

| TABLE 2-7 LINKER COMMAND FILE STACK TOKENS                    |    |

| TABLE 2-8 OS_IRQ_STACK_SIZE MODIFICATION                      |    |

| TABLE 2-9 COMMAND LINE SET OF OS_IRQ_STACK_SIZE               | 16 |

| TABLE 2-10 VARIABLES STACK NAMES                              |    |

| Table 2-11 OS_N_CORE MODIFICATION                             |    |

| TABLE 2-12 COMMAND LINE SET OF OS_N_CORE (ASM)                |    |

| TABLE 2-13 COMMAND LINE SET OF OS_N_CORE (C)                  | 17 |

| Table 2-14 OS_RUN_PRIVILEGE MODIFICATION                      |    |

| TABLE 2-15 COMMAND LINE SET OF OS_RUN_PRIVILEGE               |    |

| TABLE 2-16 OS_USE_CACHE SET-UP                                | 18 |

| TABLE 2-17 COMMAND LINE SET OF OS_USE_CACHE                   |    |

| TABLE 2-18 SATURATION BIT CONFIGURATION                       |    |

| TABLE 2-19 COMMAND LINE SET OF SATURATION BIT CONFIGURATION   |    |

| TABLE 2-20 OS_SPINLOCK SPECIFICATION                          |    |

| TABLE 2-21 COMMAND LINE SET OF OS_SPINLOCK                    | 20 |

| TABLE 2-22 OS_SPINLOCK_BASE MODIFICATION                      | 20 |

| TABLE 2-23 COMMAND LINE SET OF OS_SPINLOCK_BASE (ASM)         | 21 |

| TABLE 2-24 COMMAND LINE SET OF OS_SPINLOCK_BASE (C)           | 21 |

| TABLE 2-25 OS_SPINLOCK_DELAY MODIFICATION                     | 21 |

| TABLE 2-26 COMMAND LINE SET OF OS_SPINLOCK_DELAY (ASM)        | 21 |

| TABLE 2-27 OS_SPURIOUS_INT MODIFICATION                       | 22 |

| TABLE 2-28 COMMAND LINE SET OF OS_SPURIOUS_INT (ASM)          | 22 |

| Table 2-29 os_asm_thumb modification                          |    |

| TABLE 2-30 COMMAND LINE SET OF OS ASM THUMB (ASM)             | 23 |

| TABLE 2-31 OS_VFP_TYPE VALUES                                 | 23 |

| TABLE 2-32 OS_VFP_TYPE SETTING                                | 23 |

| TABLE 2-33 COMMAND LINE SELECTION OF NO VFP                   | 24 |

| TABLE 2-34 COMMAND LINE SELECTION OF VFP WITH 16 REGISTERS    |    |

| TABLE 2-35 COMMAND LINE SELECTION OF VFP WITH 32 REGISTERS    |    |

| TABLE 2-36 ASSEMBLY FILE MULTITHREAD CONFIGURATION            |    |

| TABLE 2-37 ASSEMBLY FILE MULTITHREAD PROTECTION ENABLING      |    |

|                                                               | 25 |

| TABLE 2-39 COMMAND LINE SET OF MULTITHREAD CONFIGURATION      |    |

| Table 2-40 os_code_sourcery modification                      | 26 |

| TABLE 2-41 COMMAND LINE SET OF OS_CODE_SOURCERY (ASM)         | 26 |

| TABLE 2-42 COMMAND LINE SET OF OS_CODE_SOURCERY (C)           | 26 |

| TABLE 3-1 COMMAND LINE SET THE INTERRUPT TABLE SIZE           | 27 |

| TABLE 3-2 ATTACHING A FUNCTION TO AN INTERRUPT.               |    |

| TABLE 3-3 INVALIDATING AN ISR HANDLER                         |    |

| TABLE 4-1 CONTEXT SAVE STACK REQUIREMENTS                     |    |

| Table 9-1 "C" Code Memory Usage                               |    |

| TABLE 9-2 ASSEMBLY CODE MEMORY USAGE                          |    |

| TABLE 9-3 MEASUREMENT WITHOUT TASK SWITCH                     |    |

| TABLE 9-4 MEASUREMENT WITHOUT BLOCKING                        |    |

| TABLE 9-5 MEASUREMENT WITH TASK SWITCH                        |    |

| TABLE 9-6 MEASUREMENT WITH TASK UNBLOCKING                    | 45 |

| Table 9-7 Latency Measurements   | 46 |

|----------------------------------|----|

| TABLE 10-1: CASE 0 BUILD OPTIONS | 47 |

| TABLE 10-2: CASE 1 BUILD OPTIONS | 48 |

| TABLE 10-3: CASE 2 BUILD OPTIONS | 49 |

| TABLE 10-4: CASE 3 BUILD OPTIONS | 50 |

| TABLE 10-5: CASE 4 BUILD OPTIONS | 51 |

| TABLE 10-6: CASE 5 BUILD OPTIONS | 52 |

| TABLE 10-7: CASE 6 BUILD OPTIONS | 53 |

| Table 10-8: Case 7 build options | 54 |

Rev 1.9 Page 7

#### 1 Introduction

This document is a complement to the user guide and it details the port of the SMP / BMP multi-core mAbassi RTOS to the ARM Cortex-A9 multi-core processor, commonly known as the Arm9 MPcore. The software suite used for this specific port is the Xilinx Software Development Kit (SDK) from Xilinx Inc.; the version used for the port and all tests is Version 14.6 build SDK\_P.68d. The GCC tool chain used for compilation, assembly and linking is the Mentor Graphics Sourcery CodeBench Lite version 2012.09-105, which is supplied as an integral part of the Xilinx SDK environment.

#### 1.1 Distribution Contents

The set of files supplied with this distribution are listed in Table 1-1 below:

| File Name                  | Description                                                                 |

|----------------------------|-----------------------------------------------------------------------------|

| mAbassi.h                  | RTOS include file                                                           |

| mAbassi.c                  | RTOS "C" source file                                                        |

| ARMv7_SMP_L1_L2_GCC.s      | L1 and L2 caches, MMU, and SCU set-up module for the MPcore A9 / GCC        |

| cmsis_os.h                 | Optional CMSIS V 3.0 RTOS API include file                                  |

| cmsis_os.c                 | Optional CMSIS V 3.0 RTOS API source file                                   |

| mAbassi_SMP_CORTEXA9_GCC.s | RTOS assembly file for the SMP ARM Cortex-A9 to use with the GCC tool chain |

|                            | Many demos                                                                  |

**Table 1-1 Distribution**

#### 1.2 Limitations

The RTOS reserves the SWI (software interrupts) numbers 0 to 6 when mAbassi is configured to operate in user mode. A hook is made available for the application to use the SWI, as long as the numbers used are above 6. This keeps mAbassi compatible with the ARM semi-hosting protocol.

#### 1.3 Features

Depending on the selected build configuration, the application can operate either in privileged or user mode. Operating in privileged mode eliminates almost all the code areas that disable interrupts, as SWIs are not required to access privileged registers or peripherals (when the processor processes a SWI, the interrupts are disabled). Selecting to run in privileged mode also generates more real-time optimal code.

Fast Interrupts (FIQ) are not handled by the RTOS, and are left untouched by the RTOS to fulfill their intended purpose of interrupts not requiring kernel access. Only the interrupts mapped to the IRQ interrupt are handled by the RTOS.

The hybrid stack is not available in this port, as ARM's GIC (Generic Interrupt Controller) does not support nesting of the interrupts (except FIQ nesting the IRQ). The ARM Cortex-A9 intrinsically supports exactly the same functionality delivered by mAbassi's hybrid stack. This is because the interrupts (IRQ) use a dedicated stack when in this processor mode.

The assembly file does not use the BL addr when calling a function. This was chosen to allow the assembly file to access the whole 4 GB address space.

The VFPv3 or VPFv3D16, and NEON floating-point peripherals are supported by this port, and their registers are saved as part of the task context save and the interrupt context save.

Rev 1.9 Page 9

#### 2 Target Set-up

Very little is needed to configure the Xilinx Software Development Kit environment to use the mAbassi RTOS in an application. All there is to do is to add the files mAbassi.c and mAbassi\_SMP\_CORTEXA9\_GCC.s in the makefile of the application project, and make sure the configuration settings in the file mAbassi\_SMP\_CORTEXA9\_GCC.s (described in the following subsections) match to the needs of the application. As well, update the include file path in the C/C++ compiler preprocessor options with the location of mAbassi.h. There is no need to include a start-up file, as the file mAbassi\_SMP\_CORTEXA9\_GCC.s takes care of all the start-up operations required for an application to operate on a multi-core processor.

NOTE: The document describes the settings for different platforms, many of which are not Xilinx devices. The reason for this is the assembly file madassi\_SMP\_CORTEX\_A9\_GCC.s, used for the GCC tool chain, is shared amongst multiple development platforms. Therefore any information related to non-Xilinx devices should not be used and can simply be ignored.

#### 2.1 Build Options (GUI)

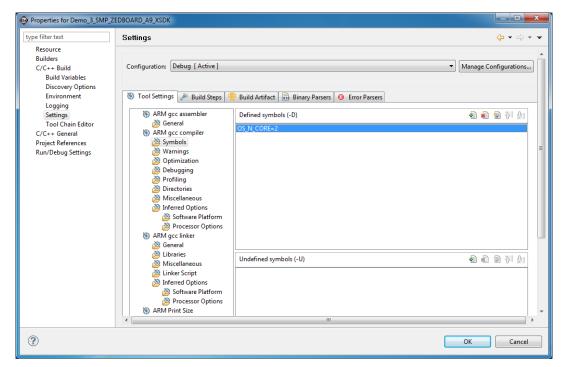

In the following section, all build option examples are given using command line commands, as they would be used in a makefile. It is quite likely the application project will be based on the SDK GUI and not a custom makefile. All build options, either for the compiler, the assembler, or for both, can also be defined through the SDK GUI. Taking for example the build option OS\_N\_CORE, it can be passed to the compiler using the GUI by moving across the following menus / options:

Properties  $\rightarrow$  C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  ARM gcc compiler  $\rightarrow$  Symbols

By clicking on the *Add*... icon and inserting the statement, for example, OS\_N\_CORE=2 in the pop-up box. This is shown in the following figure:

Figure 2-1: "C" build option setting

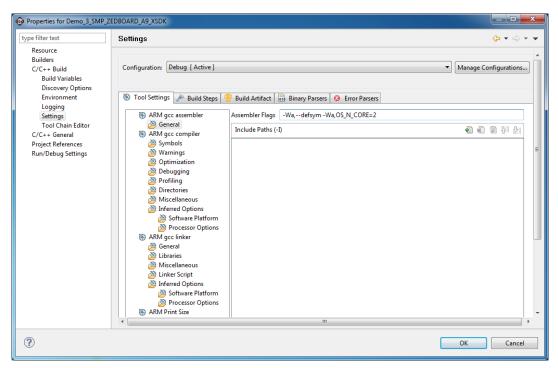

In the case of the assembler, the default command for assembly is arm-xilinx-eabi-gcc, which is the compiler and not the assembler itself (arm-xilinx-eabi-as). This means the compiler must be informed about the fact it has to pass the information to the assembler. This is done through the -Wa command line option of the compiler. For example, to set the build option OS\_N\_CORE for the assembler, the command line option to use is shown in the following table:

Table 2-1 Assembly build options passed through the compiler

```

arm-xilinx-eabi-gcc ... -Wa,--defsym -Wa,OS_N_CORE=2 ...

```

This is specified using the GUI by moving across the following menus / options:

Properties  $\rightarrow$  C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  ARM gcc assembler  $\rightarrow$  General

And inserting information in the Assembler Flags box as shown in the following figure:

Figure 2-2: "ASM" build option setting (through "GCC")

Instead of using the compiler for assembly, it is possible to use the assembler directly. To make the GUI use the assembler directly, go through the following menus / options:

Properties

$$\rightarrow$$

C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  ARM gcc assembler

And replace arm-xilinx-eabi-gcc to arm-xilinx-eabi-as in the *Command* box. This is shown in the following figure:

Figure 2-3: Using the assembler in the GUI

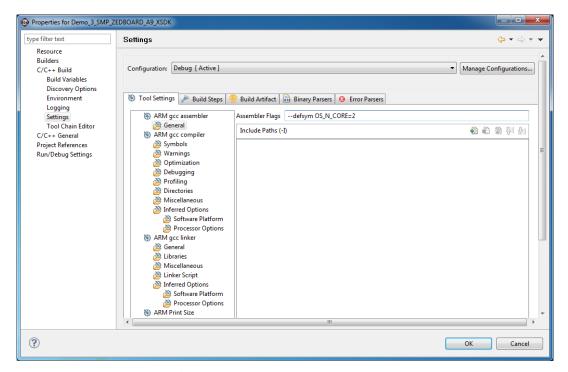

If the assembler is used in the GUI instead of the compiler, there is no need to use the —wa option, as this option is only needed when using the compiler. For example, to set the build option os\_N\_core for the assembler, the command line option to use is shown in the following table:

Table 2-2 Assembly build options passed through the assembler

```

arm-xilinx-eabi-as ... --defsym OS_N_CORE=2 ...

```

This is specified using the GUI by moving across the following menus / options:

Properties  $\rightarrow$  C/C++ Build  $\rightarrow$  Settings  $\rightarrow$  ARM gcc assembler  $\rightarrow$  General

And inserting the information in the Assembler Flags box as shown in the following figure:

Figure 2-4: "ASM" build option setting (through "AS")

#### 2.2 Target Device

Each manufacturer uses a different method to release from reset the cores other than core #0. As such, the start-up code must to be tailored for each target device. This information is specified in the assembly file with the value assigned to the token OS\_PLATFORM. At the time of writing this document, the following platforms are supported:

| Target Platform               | os_platform value          |

|-------------------------------|----------------------------|

| Altera / Arria V Soc FPGA     | 0xAAC5 (Same as Cyclone V) |

| Altera / Cyclone V Soc FPGA   | 0xAAC5 (Same as Arria V)   |

| Texas Instruments / OMAP 4460 | 0x4460                     |

| Xilinx / Zynq XC7Z020         | 0x7020                     |

| Freescale i.MX6               | 0xFEE6                     |

Table 2-3 OS\_PLATFORM valid settings

If in the future if there are platforms that are not listed in the above table, the numerical values assigned to the platform are specified in comments in the file madassi\_SMP\_CORTEXA9\_GCC.s., right beside the internal definition of OS\_PLATFORM (around line 85).

To select the target platform, all there is to do is to change the numerical value associated with the token OS\_PLATFORM located around line 85 in the file madassi\_SMP\_CORTEXA9\_GCC.s. By default, the target platform is the Xilinx Zynq XC7Z020, therefore OS\_PLATFORM is assigned the numerical value 0x7020. The following table shows how to set the target platform to the Altera Cyclone V, which is assigned the numerical value 0xAAC5:

#### Table 2-4 os platform modification

```

#ifndef OS_PLATFORM

.ifndef OS_PLATFORM

.equ OS_PLATFORM, 0xAAC5

.endif

#endif

```

Alternatively, it is possible to overload the OS\_PLATFORM value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the target platform numerical value:

Table 2-5 Command line set of OS\_PLATFORM

```

arm-xilinx-eabi-as ... --defsym OS_PLATFORM=0xAAC5 ...

```

#### 2.3 Stacks Set-up

The Cortex-A9 processor uses 6 individual stacks, which are selected according to the processor mode. The following table describes each stack and the build token used to define the size of the associated stack:

| Description         | Token Name          |

|---------------------|---------------------|

| User / System mode  | N/A                 |

| Supervisor mode     | OS_SUPER_STACK_SIZE |

| Abort mode          | OS_ABORT_STACK_SIZE |

| Undefined mode      | OS_UNDEF_STACK_SIZE |

| Interrupt mode      | OS_IRQ_STACK_SIZE   |

| Fast Interrupt mode | OS_FIQ_STACK_SIZE   |

**Table 2-6 Stack Size Tokens**

The User / System mode stack is defined as the symbol \_\_cs3\_stack (or \_\_stack depending on the target platform) in the linker command. That linker-set stack is assigned to the Adam & Eve task, which is the element of code executing upon start-up on core #0. The other cores start by entering the functions COREstartN(), which are fully described in the mAbassi User's Guide [R1], and their stack sizes are defined as part of the mAbassi standard build options.

The other stack sizes are individuality controlled by the values set by the OS\_?????\_STACK\_SIZE definitions, located between lines 50 and 70 in the file mAbassi\_SMP\_CORTEXA9\_GCC.s. To not reserve a stack for a processor mode, all there is to do is to set the definition of OS\_?????\_STACK\_SIZE to a value of zero (0). To specify the stack size, the definition of OS\_?????\_STACK\_SIZE is set to the desired size in bytes (see Section 4 for more information on stack sizing). Note that each core on the device (up to the number specified by the build option OS\_N\_CORE) will use the same stack sizes for a processor mode: this is the value assigned to the token OS\_?????\_STACK\_SIZE. This equal distribution of stack size may not be optimal; if a non-equal distribution is required, contact Code Time Technologies for additional information on the code modifications involved.

Alternatively, it is possible to use definitions of the stack extracted from the linker command file. When the value assigned to a stack definition token OS\_?????\_STACK\_SIZE is set to -1, the stack uses the size and the data section reserved in the linker command file; then no memory is reserved for this stack by the file Abassi\_SMP\_CORTEXA9\_GCC.s. Contrary to setting the definition token to a positive value, the stack size defined in the linker is the total stack size shared by all cores (except for OS\_STACK\_SIZE / \_\_stack). This means for 2 cores, each core will be allocated half the stack size defined in the linker command file; for 4 cores, each core will be allocated a quarter of the stack size defined in the linker command file. The names of the base of the stack (which is at the highest memory address of data section) and the names of their sizes are listed in Table 2-7.

| Description         | Stack Name       | Stack Size Name              |

|---------------------|------------------|------------------------------|

| User / System mode  | cs3_stack        | _STACK_SIZE                  |

| Supervisor mode     | supervisor_stack | _SUPERVISOR_STACK_SIZE       |

| Abort mode          | abort_stack      | _ABORT_STACK_SIZE            |

| Undefined mode      | undef_stack      | _UNDEF_STACK_SIZE            |

| Interrupt mode      | irq_stack        | _IRQ_STACK_SIZE <sup>1</sup> |

| Fast Interrupt mode | fiq_stack        | _FIQ_STACK_SIZE              |

**Table 2-7 Linker Command file Stack Tokens**

As supplied in the distribution, all stack size tokens are assigned the value of -1 meaning all stack information is supplied by the linker command file.

To modify the size of a stack, taking the IRQ stack for example and reserving a stack size of 256 bytes for each core for the IRQ processor mode, all there is to do is to change the numerical value associated with the token; this is shown in the following table:

Table 2-8 os\_irq\_stack\_size modification

```

#ifndef OS_IRQ_STACK_SIZE

.ifndef OS_IRQ_STACK_SIZE

.equ OS_IRQ_STACK_SIZE, 256

.endif

#endif

```

<sup>&</sup>lt;sup>1</sup> For versions pre-1.64.62: the size of the IRQ stack is the same as the one for main(). This setting originally comes from the standard Xilinx Zynq linker command file definitions. It is retained because the file mAbassi\_SMP\_CORTEX\_GCC.s is common to all GCC tool chains. If necessary, it is straightforward to change.

Alternatively, it is possible to overload the OS\_?????\_STACK\_SIZE value set in mabassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option ——defsym and specifying the desired stack size as shown in the following example, where the IRQ stack size is set to 512 bytes:

Table 2-9 Command line set of OS\_IRQ\_STACK\_SIZE

```

arm-xilinx-eabi-as ... --defsym OS_IRQ_STACK_SIZE=512 ...

```

A third way to allocate the different stacks and specify their sizes is by setting to a value of -2 the token os\_?????\_stack\_size. When this is done, the stacks memory and their sizes are supplied through external arrays and variables. The stack arrays must be dimensioned to: #Core \* stacksize bytes; the run-time set-up of the stacks makes sure the stacks are aligned according to the Cortex-A9 requirements. The variable specifying the stack sizes indicates the number of bytes per core and not the number of bytes in the stack array.

**Description Stack Name** Stack Size Name User / System mode n/a n/a Supervisor mode G SUPER stack G SUPER stackSize Abort mode G\_ABORT\_stack G\_ABORT\_stackSize G\_UNDEF\_stack G UNDEF stackSize Undefined mode Interrupt mode G\_IRQ\_stack G\_IRQ\_stackSize G\_FIQ\_stack G FIQ stackSize Fast Interrupt mode

**Table 2-10 Variables Stack Names**

#### 2.4 Number of cores

When operating the mAbassi RTOS on a platform, the RTOS needs to be configured for the number of cores it has access to, or will use. This number is most of the time the same as the number of cores the device has, but it also can be set to a value less than the total number of cores on the device, but not larger obviously. This must be done for both the mAbassi.c file and the mAbassi\_SMP\_CORTEXA9\_GCC.s file, through the setting of the build option os\_N\_CORE. In the case of the file mAbassi.c, os\_N\_CORE is one of the standard build options. In the case of the file mAbassi\_SMP\_CORTEXA9\_GCC.s, to modify the number of cores, all there is to do is to change the numerical value associated to the token definition of os\_N\_CORE, located around line 35; this is shown in the following table. By default, the number of cores is set to 2.

Table 2-11 os n core modification

```

#ifndef OS_N_CORE

.ifndef OS_N_CORE

.equ OS_N_CORE, 4

.endif

#endif

```

Alternatively, it is possible to overload the OS\_N\_CORE value set in madassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required number of cores as shown in the following example, where the number of cores is set to 4:

Table 2-12 Command line set of OS\_N\_CORE (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_N_CORE=4 ...

```

Exactly the same value of OS\_N\_CORE as specified for the assembler must be specified for the compiler; a mismatch between the assembly and "C" definition either generates a link error if the assembly file value is less than the "C" value or will freeze the application if the assembly file value is larger than the "C" value. In the following example, the number of cores is set to 4 for the "C" files:

Table 2-13 Command line set of OS\_N\_CORE (C)

```

arm-xilinx-eabi-gcc ... -D OS_N_CORE=4 ...

```

NOTE: mAbassi can be configured to operate as the single core Abassi by setting os\_N\_core to 1, or setting os\_MP\_TYPE to 0 or 1. When configured for single core on the Cortex-A9 MPCore, the single core application always executes on core #0.

#### 2.5 Privileged mode

It is possible to configure mAbassi for the Cortex-A9 MPCore to make the application execute in either the USER processor mode (un-privileged) or in the SYS processor mode (privileged). Having the application executing in the SYS processor mode (privileged) delivers two main advantages over having it executing in the USER mode (un-privileged). The first one is, when in the USER mode, Software interrupts (SWI) are needed to read or write the registers and peripherals that are only accessible in privileged mode. Having to use SWI disables the interrupts during the time a SWI is processed. The second advantage of executing the application in SYS mode is again related to the SWI, but this time it is one of CPU efficiency: the code required to replace the functionality of the SWI is much smaller, therefore less CPU is needed to execute the same operation.

There is no fundamental reason why an application should be executing in the un-privileged mode with mAbassi. First, even though the mAbassi kernel is a single function, it always executes within the application context. There are no service requests, alike the Arm9 SWI, involved to access the kernel. And second, mAbassi was architected to be optimal for embedded application, where the need to control accesses to peripherals or other resources, as in the case of a server level OS, is not applicable.

Only the file madassi\_SMP\_CORTEXA9\_GCC.s (ARM\_SMP\_L1\_L2\_GCC.s, release version 1.69.69 and upward, also needs this information) requires the information if the application executes in the privileged mode or not. By default, the distribution file sets the processor to operate in privileged mode. To select if the application executes in privileged mode or not, all there is to do is to change the value associated to the definition of the token OS\_RUN\_PRIVILEGE, located around line 40. Associating a numerical value of zero to the build option configures mAbassi to let the application execute in the USER processor mode, which is un-privileged:

#### Table 2-14 OS\_RUN\_PRIVILEGE modification

```

#ifndef OS_RUN_PRIVILEGE

.ifndef OS_RUN_PRIVILEGE

.equ OS_RUN_PRIVILEGE, 0

.endif

#endif

```

Alternatively, it is possible to overload the OS\_RUN\_PRIVILEGE value set in madassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the desired mode of execution as shown in the following example, where the selected mode is non-privilege:

Table 2-15 Command line set of OS\_RUN\_PRIVILEGE

```

arm-xilinx-eabi-as ... --defsym OS_RUN_PRIVILEGE=0 ...

```

#### 2.6 L1 & L2 Cache Set-up

The build option OS\_USE\_CACHE controls if the MPcore L1 and L2 caches, the memory management unit (MMU) and the snoop control unit (SCU) are configured and enabled. Setting the token OS\_USE\_CACHE to a non-zero value configures and enables the caches, MMU and SCU; setting it to a value of zero (0) disables the caches, MMU and SCU. The OS\_USE\_CACHE token is defined around line 120 in the file madassi\_SMP\_CORTEXA9\_GCC.s and is set to enable (non-zero) by default. This is shown in the following table:

Table 2-16 os\_use\_cache set-up

```

#ifndef OS_USE_CACHE

.ifndef OS_USE_CACHE

.equ OS_USE_CACHE, 0

.endif

#endif

```

Alternatively, it is possible to overload the OS\_USE\_CACHE value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the desired mode of execution as shown in the following example, where the selected mode is non-privileged:

Table 2-17 Command line set of OS\_USE\_CACHE

```

arm-xilinx-eabi-as ... --defsym OS_USE_CACHE=0 ...

```

NOTE: When the caches are used, there is a dependency on the external function COREcacheON(). This function is located in the file ARMv7\_SMP\_L1\_L2\_GCC.s file, which is optional.

#### 2.7 Saturation Bit Set-up

In the ARM Cortex-A9 status register, there is a sticky bit to indicate if an arithmetic saturation or overflow has occurred during a DSP instruction; this is the Q flag in the status register (bit #27). By default, this bit is not kept localized at the task level, as extra processing is required during the task context switch to do so; instead, it is propagated across all tasks. This choice was made because most applications do not care about the value of this bit.

If this bit is relevant for an application, even for a single task, then it must be kept local to each task. To keep the value of the saturation bit localized, the token OS\_HANDLE\_PSR\_Q must be set to a non-zero value; to disable the localization, it must be set to a zero value. This is located at around line 50 in the file madassi\_SMP\_CORTEXA9\_GCC.s. The distribution code disables the localization of the Q bit, setting the token HANDLE PSR Q to zero, as shown in the following table:

**Table 2-18 Saturation Bit configuration**

```

#ifndef OS_HANDLE_PSR_Q

.ifndef OS_HANDLE_PSR_Q

.equ OS_HANDLE_PSR_Q, 0

.endif

#endif

```

Alternatively, it is possible to overload the OS\_HANDLE\_PSR\_Q value set in mabassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the desired setting (here is to keep localized) with the following:

Table 2-19 Command line set of Saturation Bit configuration

```

arm-xilinx-eabi-as ... --defsym OS_HANDLE_PSR_Q=1 ...

```

#### 2.8 Spinlock implementation

All multi-core SMP RTOSes require the use of spinlocks to provide a short time exclusive access to shared resources. mAbassi internally uses two functions to lock and unlock the spinlocks, CORELOCK() and COREunlock() (refer to mAbassi User's Guide [R1]), and these functions are implemented in the mAbassi\_SMP\_CORTEXA9\_GCC.s file. The spinlocks can be implemented using 3 different techniques:

- > Pure software spinlock

- ➤ Using the LDREX and STREX instructions

- ➤ Using a hardware spinlock register

The difference between the 3 types of spinlocks can be resumed as follows:

- A pure software spinlock disables the interrupts for a short time but does not depend on any hardware resources nor peripherals

- The LDREX/STREX based spinlock does not disable the interrupts but the ARM Snoop Control Unit (SCU) must be enabled, which implies the D-Cache must be configured and enabled which in turn requires the Memory Management Unit (MMU) to be configured and enabled

- The hardware register spinlock does not disable the interrupts, uses less code than the pure software spinlock, but it uses more code than the LDREX/STREX based spinlock. This type of spinlock can only be used f the device has custom spinlock registers

The type of spinlock to use is specified with the token the token OS\_SPINLOCK. It must be set to zero (0) for a pure software spinlock, one (1) for the LDREX/STREX based spinlock, or, for a hardware register base spinlock, to the same value as the token OS\_PLATFORM (Section 2.2) when the target device supports hardware spinlocks.

NOTE: If the token OS\_SPINLOCK is set to one (1) for the LDREX / STREX based spinlock and the cache is not enabled (Section 2.6), an assembly time error message is issued.

The distribution code uses the pure software spinlock, meaning the OS\_PLATFORM token is set to zero, as shown in the following table. This is located around line 90 in the file madassi\_SMP\_CORTEXA9\_GCC.s:

#### Table 2-20 os\_spinlock specification

```

#ifndef OS_SPINLOCK

.ifndef OS_SPINLOCK

.equ OS_SPINLOCK, 0

.endif

#endif

```

It is possible to overload the OS\_SPINLOCK value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the type of spinlock as shown in the following example, where the spinlock is set to use the LDREX/STREX pair of instructions:

Table 2-21 Command line set of OS SPINLOCK

```

arm-xilinx-eabi-as ... --defsym OS_SPINLOCK=1 ...

```

Some target platforms have sets of hardware spinlock registers, e.g. Texas Instruments OMAP 4460. When the selected spinlock implementation is based on the hardware spinlock registers, mAbassi reserves a total of 4 spinlock registers. By default, the spinlock register indexes #0 to #5 are used by mAbassi and as such must not be used by anything else. If mAbassi needs to co-exist with other applications that are already using one or more registers in this set of 4, it is possible to make mAbassi use a different set of indexes. The base index of the set of 4 registers is specified with the value assigned to the token os\_spinlock\_base. The assembly file and the "C" file use same token and they must be set to the same value. As an example to make mAbassi use the hardware registers #22 to #27, all there is to do is to change the numerical value associated to the os\_spinlock\_base token, located around line 100; this is shown in the following table:

Table 2-22 os spinlock base modification

```

#ifndef OS_SPINLOCK_BASE

.ifndef OS_SPINLOCK_BASE

.equ OS_SPINLOCK_BASE, 22

.endif

#endif

```

It is also possible to overload the OS\_SPINLOCK\_BASE value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required base register index as shown in the following example:

Table 2-23 Command line set of OS\_SPINLOCK\_BASE (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_SPINLOCK_BASE=22 ...

```

The same numerical value must also be provided to the "C" file. This is show in the following table:

Table 2-24 Command line set of OS\_SPINLOCK\_BASE (C)

```

arm-xilinx-eabi-gcc ... --DOS_SPINLOCK_BASE=22 ...

```

There is a possible race condition when using spinlocks on a target processor with 3 or more cores. This is the corner case when the tasks running on 3 cores or more are all trying non-stop to lock and unlock the same spinlock. When this condition arises, it is possible that the same 2 cores always get the spinlock, starving the other one(s). This is not an issue with mAbassi but it is due to the fact the memory accesses (S/W spinlock or H/W spinlock) and the cache give access based on the core numbering and not in a round robin or random fashion. To randomize the core given the spinlock, a random delay can be added when the number of cores (OS\_N\_CORES) is greater than 2. The delay is added when the build option OS\_SPINLOCK\_DELAY is set to a non-zero value and OS\_N\_CORE is greater than 2; by default, the token OS\_SPINLOCK\_DELAY is set to a non-zero value. As for other tokens, the numerical value associated to the OS\_SPINLOCK\_DELAY token, located around line 90, can be changed as shown in the following table:

Table 2-25 os spinlock delay modification

```

#ifndef OS_SPINLOCK_DELAY

.ifndef OS_SPINLOCK_DELAY

.equ OS_SPINLOCK_DELAY, 0

.endif

#endif

```

It is also possible to overload the OS\_SPINLOCK\_DELAY value set in madassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required base register index as shown in the following example:

Table 2-26 Command line set of os SPINLOCK DELAY (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_SPINLOCK_DELAY=0 ...

```

#### 2.9 Spurious Interrupt

The Cortex-A9 interrupt controller (GIC) generates an interrupt when a spurious interrupt is detected. The interrupt number for a spurious interrupt is 1023 and it cannot be disabled. When mAbassi is configured to handle less than 1024 interrupt sources (set by the build option OS\_N\_INTERRUPTS), then if a spurious interrupt occurs, the function pointer of the handler read from the interrupt table is invalid, as the interrupt table is not large enough to hold an entry for it. The build option OS\_SPURIOUS\_INT (new in version 1.66.65) can be set to inform the interrupt dispatcher to ignore interrupt #1023. The special handling of the spurious interrupt is enabled when the build option OS\_SPURIOUS\_INT is set to a non-zero value; by default, the token OS\_SPURIOUS\_INT is set to a non-zero value, enabling the special handling. As for other tokens, the numerical value associated to the OS\_SPURIOUS\_INT token, located around line 130, can be changed as shown in the following table:

Table 2-27 os spurious int modification

```

#ifndef OS_SPURIOUS_INT

.ifndef OS_SPURIOUS_INT

.equ OS_SPURIOUS_INT, 0

.endif

#endif

```

It is also possible to overload the OS\_SPURIOUS\_INT value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required base register index as shown in the following example:

Table 2-28 Command line set of os spurious int (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_SPURIOUS_INT=0 ...

```

Unless the build option os\_N\_INTERRUPTS is set to 1024, the build option os\_Spurious\_INT should never be set to a value of zero. The real-time and code size impact of including the spurious interrupt special handling is very minimal: it adds 1 instruction when using 32-bit ARM instructions and 2 instructions with Thumb2.

#### 2.10 Thumb2

The assembly support file (madassi\_SMP\_CORTEXA9\_GCC.s) is by default using 32-bit ARM instructions. The build option os\_asm\_thumb (new in version 1.66.66) can be set to use Thumb2 instructions instead. The use of Thumb2 instructions is enabled when the build option os\_asm\_thumb is set to a non-zero value; by default, the token os\_asm\_thumb is set to a non-zero value, enabling the special handling. As for other tokens, the numerical value associated to the os\_asm\_thumb token, located around line 135, can be changed as shown in the following table:

Table 2-29 os\_asm\_thumb modification

```

#ifndef OS_ASM_THUMB

.ifndef OS_ASM_THUMB

.equ OS_ASM_THUMB, 1

.endif

#endif

```

It is also possible to overload the OS\_ASM\_THUMB value set in mAbassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required base register index as shown in the following example:

Table 2-30 Command line set of os ASM THUMB (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_ASM_THUMB=1 ...

```

NOTE: Never use the --thumb command line option with the madassi SMP CORTEXA9 GCC.s file.

#### 2.11 VFP / NEON set-up

When a processor is coupled with a floating-point peripheral and this VFP is used by the application code, then mAbassi must be informed it must preserve the VFP register during the task context switch and the interrupt context save. As such, the type of VFP mAbassi must handle needs to match the one the compiler is set to use. A mismatch will quite likely make the application misbehave. The type of floating-point peripheral is specified to Abassi through the assembly file mAbassi\_SMP\_CORTEXA9\_GCC.s, which depending on its configuration can handle three different types of floating-point peripherals. They are:

- ➤ No VFP coprocessor

- > VFPv2 / VFPv3D16 / Neon with 16 registers

- ➤ VFPv3 / Neon with 32 registers

The type of FPU to support is specified in the madassi\_SMP\_CORTEXA9\_GCC.s file, with the build option os\_vfp\_type. The value assigned to os\_vfp\_type is the number of 64 bit registers the VFP possesses. The valid values for os vfp\_type are:

| FPU      | OS_VFP_TYPE value |

|----------|-------------------|

| No FPU   | 0                 |

| VFPv2    | 16                |

| VFPv3D16 | 16                |

| VFPv3    | 32                |

| Neon     | 32                |

Table 2-31 os VFP TYPE values

By default, the token OS\_VFP\_TYPE is set to a value of 32 indicating to mAbassi to support a floating-point peripheral with 32 64-bit registers. The following table shows the default setting of the token OS\_VFP\_TYPE in file mAbassi\_CORTEXA9\_GCC.s around line 105:

Table 2-32 os\_vfp\_type setting

```

#ifndef OS_VFP_TYPE

.ifndef OS_VFP_TYPE

.equ OS_VFP_TYPE, 32

.endif

#endif

```

The VFP type can be changed directly in the file madassi\_CORTEXA9\_GCC.s, by changing the assigned numerical value. Also, the value internally assigned in madassi\_CORTEXA9\_GCC.s can be overloaded through the command line option to the assembler.

Rev 1.9 Page 23

The following 3 tables show the command line setting for each of the supported floating-point units:

#### Table 2-33 Command line selection of no VFP

```

arm-xilinx-eabi-as ... --defsym OS_VFP_TYPE=0 ...

```

#### Table 2-34 Command line selection of VFP with 16 registers

```

arm-xilinx-eabi-as ... --defsym OS_VFP_TYPE=16 ...

```

#### Table 2-35 Command line selection of VFP with 32 registers

```

arm-xilinx-eabi-as ... --defsym OS_VFP_TYPE=32...

```

#### 2.12 Multithreading

For a complete description of the multi-threading protection mechanisms, refer to the Library reentrance protection document [R4].

NOTE: When the application is compiled using the Thumb instruction set then the reentrance and the multithreading protections are not supported by the Red Hat's Newlib. This is not a limitation of mAbassi but a restriction of the pre-compiled library itself. A compile time error message is generated if the Thumb instruction set is used when the reentrance and multithreading protections are enabled.

The build option can be set directly in the assembly file; this is located at around line 115 in the file madassi\_SMP\_CORTEXA9\_GCC.s. The distribution code disables the multithreading and reentrance protections, setting the token OS NEWLIB REENT to zero, as shown in the following table:

Table 2-36 Assembly file multithread configuration

```

#ifndef OS_NEWLIB_REENT

.ifndef OS_NEWLIB_REENT

.equ OS_NEWLIB_REENT, 0

.endif

#endif

```

To enable the full multithreading and reentrance protections, set the value of OS\_NEWLIB\_REENT to a positive value as shown in the following table:

Table 2-37 Assembly file multithread protection enabling

```

#ifndef OS_NEWLIB_REENT

.ifndef OS_NEWLIB_REENT

.equ OS_NEWLIB_REENT, 1

.endif

#endif

```

Alternatively, it is possible to overload the OS\_NEWLIB\_REENT value set in the file madassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the desired setting with the following:

#### Table 2-38 Command line set of multithread configuration

```

arm-xilinx-eabi-as ... --defsym OS_NEWLIB_REENT=1 ...

```

The exact same definition of OS\_NEWLIB\_REENT as the one specified for the assembler (either directly or through the command line) must be must be given to the compiler. This can be done with the command line option -D and specifying the setting with the following:

Table 2-39 Command line set of multithread configuration

```

arm-xilinx-eabi-gcc ... -DOS_NEWLIB_REENT=1 ...

```

A little more than one (1) kilobyte per task is needed to support multithreading protection. This extra memory is not an integral part of the task descriptor; instead a pointer in the task descriptor holds the location of this per task extra memory. The one (1) kilobyte per task is allocated using the component OSalloc(), which means either enough memory must be reserved with OS\_ALLOC\_SIZE or, if OS\_ALLOC\_SIZE is set to zero, enough heap area must be reserved for malloc().

#### 2.13 Performance Monitoring

New in version 1.69.69, is the performance monitoring add-on. This facility relies on a fine resolution timer / counter and this timer / counter is set-up and handled in the file madassi\_SMP\_CORTEXA9\_GCC.s. There are 3 build options related to the performance monitoring timer / counter:

- OS\_PERF\_TIMER\_BASE

- > OS PERF TIMER DIV

- > OS\_PERF\_TIMER\_ISR

All Cortex-A9 MPCores have a global timer / counter and it is a natural candidate to be used by the performance monitoring add-on. To use the global timer / counter, set the build option OS\_PERF\_TIMER\_BASE to a value of 0. If the pre-scaling value of the global timer / counter is set in the application, then set the build option OS\_PERF\_TIMER\_DIV to a value of 0. If the prescaler is not set by the application, then set build option OS\_PERF\_TIMER\_DIV to the desired prescaler value. For the global timer / counter, the build option OS\_PERF\_TIMER\_ISR is ignored as it does not requires interrupts as it is a 64-bit timer (64 bits is the size of the counters used by the performance monitoring add-on).

For other counter / timer options, please look directly into the file madassi\_SMP\_CORTEXA9\_GCC.s, searching for the OS\_PERF\_TIMER\_BASE token. There is a very detailed table explaining all the offerings and specifying the values to set the 3 related build options to for each the timer / counter supported.

#### 2.14 Code Sourcery / Yagarto

There are two main trunks of the GCC for ARM; one is maintained by Mentor Graphics and is named Code Sourcery, the other was originally named Yagarto, with Atollic, for example, using this variant. There are small differences between the two that are related to the start-up code and the "C" library. Both variants are supported as indicated through the token os\_code\_sourcery. By default, this token is set to a non-zero value to fulfill the start-up and library requirements of the Code Sourcery variant. If the Yagarto variant is used instead, the token os\_code\_sourcery must be set to a value of zero; this is shown in the following table where the code snippet is located around line 125:

Table 2-40 os\_code\_sourcery modification

```

#ifndef OS_CODE_SOURCERY

.ifndef OS_CODE_SOURCERY

.equ OS_CODE_SOURCERY, 0

.endif

#endif

```

It is also possible to overload the OS\_SPINLOCK\_DELAY value set in mabassi\_SMP\_CORTEXA9\_GCC.s by using the assembler command line option --defsym and specifying the required base register index as shown in the following example:

Table 2-41 Command line set of os CODE SOURCERY (ASM)

```

arm-xilinx-eabi-as ... --defsym OS_CODE_SOURCERY=0 ...

```

The same numerical value must also be provided to the "C" file. This is show in the following table:

Table 2-42 Command line set of os CODE SOURCERY (C)

```

arm-xilinx-eabi-gcc ... --DOS_CODE_SOURCERY=0 ...

```

#### 2.15 Section Naming

It is possible to select between 3 type of linker section naming for the code and data from the RTOS assembly file mabassi\_SMP\_CORTEXA9\_GCC.s. The build option OS\_SECT\_NAMES controls the naming. If this build option is not defined or defined and set to a zero value, the code, R/O data and R/W sections are respectively named .text, .data and .bss. If the build option OS\_SECT\_NAMES is defined and set to a negative value, the sections are named .text.mabassi, .data.mabassi and .bss.mabassi. If instead the built option is defined and set to a positive value, the sections are named .text.FctName, .data.FctName and .bss.FctName, where FctName is the name of the function (this is identical to the way the compiler names the section).

#### 3 Interrupts

The mAbassi RTOS needs to be aware when kernel requests are performed inside or outside an interrupt context. For all IRQ sources the mAbassi RTOS provides an interrupt dispatcher, which allows it to be interrupt-aware. This dispatcher achieves two goals. First, the kernel uses it to know if a request occurs within an interrupt context or not. Second, using this dispatcher reduces the code size, as all interrupts share the same code for the decision making of entering the kernel or not at the end of the interrupt.

The distribution makes provision for 256 sources of interrupts, as specified by the token OX\_N\_INTERRUPTS in the file madassi.h<sup>2</sup>, and the value of OX\_N\_INTERRUPTS is the internal default value used by madassi.c. Even though the Generic Interrupt Controller (GIC) peripheral supports a maximum of 1020 interrupts, it was decided to set the distribution value to 256, as this seems to be a typical maximum supported by the different devices on the market.

#### 3.1 Interrupt Handling

#### 3.1.1 Interrupt Table Size

Most devices do not require all 256 interrupts, as they may only handle between 64 and 128 sources of interrupts; or some very large device may require more than 256. The interrupt table can be easily reduced to recover data space. All there is to do is to define the build option OS\_N\_INTERRUPTS (OS\_N\_INTERRUPTS is used to overload mAbassi internal value of OX\_N\_INTERRUPTS) to the desired value. This can be done by using the compiler command line option -D and specifying the desired setting with the following:

Table 3-1 Command line set the interrupt table size

```

arm-xilinx-eabi-gcc ... -D=OS_N_INTERRUPTS=49 ...

```

#### 3.1.2 Interrupt Installer

Attaching a function to a regular interrupt is quite straightforward. All there is to do is use the RTOS component OSisrInstall() to specify the interrupt number and the function to be attached to that interrupt number. For example, Table 3-2 shows the code required to attach the private timer interrupt on an ARM MPcore processor (Interrupt ID #29) to the RTOS timer tick handler (TIMtick):

Table 3-2 Attaching a Function to an Interrupt

<sup>&</sup>lt;sup>2</sup> This is located in the port-specific definition area.

At start-up, once OSstart() has been called, all OS\_N\_INTERRUPTS (truly OX\_N\_INTERRUPTS if not overloaded) interrupt handler functions are set to a "do nothing" function, named OSinvalidISR(). If an interrupt function is attached to an interrupt number using the OSisrInstall() component <u>before</u> calling OSstart(), this attachment will be removed by OSstart(), so OSisrInstall() should never be used before OSstart() has executed. When an interrupt handler is removed, it is very important and necessary to first disable the interrupt source, then the handling function can be set back to OSinvalidISR(). This is shown in Table 3-3:

Table 3-3 Invalidating an ISR handler

```

#include "mAbassi.h"

...

/* Disable the interrupt source */

OSisrInstall(Number, &OSinvalidISR);

...

```

When an application needs to disable/enable the interrupts, the RTOS supplied functions OSdint() and OSeint() should be used.

The interrupt number, as reported by Generic Interrupt Controller (GIC), is acknowledged by the ISR dispatcher, but the dispatcher does not remove the request by a peripheral if the peripheral generate a level interrupt. The removal of the interrupt request must be performed within the interrupt handler function.

One has to remember the mAbassi interrupt table is shared across all the cores. Therefore, if the same interrupt number is used on multiple cores, but the processing is different amongst the cores, a single function to handle the interrupt must be used in which the core ID controls the processing flow. The core ID is obtained through the COREGETID() component of mAbassi. One example of such situation is if the private timer is used on each of two cores, but each core private timer has a different purpose, e.g.:

- 1- on one core, it is the RTOS timer base

- 2- on the other core, it is the real-time clock tick.

At the application level, when the core ID is used to select specific processing, a critical region exists that must be protected by having the interrupts disabled (see mAbassi User's Guide [R1]). But within an interrupt handler, as nested interrupts are not supported for the Cortex-A9, there is no need to add a critical region protection, as interrupts are disabled when processing an interrupt.

#### 3.2 Fast Interrupts

Fast interrupts are supported on this port as the FIQ interrupts. The ISR dispatcher is designed to only handle the IRQ interrupts. A default do-nothing FIQ handler is supplied with the distribution; the application can overload the default handler (Section 7.2).

#### 3.3 Nested Interrupts

Interrupt nesting, other than a FIQ nesting an IRQ, is not supported on this port. The reason is simply based on the fact the Generic Interrupt Controller is not a nested controller. Also, supporting nesting on this processor architecture becomes real-time inefficient as the processor interrupt context save is not stack based, but register bank based.

#### 4 Stack Usage

The RTOS uses the tasks' stack for two purposes. When a task is blocked or ready to run but not running, the stack holds the register context that was preserved when the task got blocked or preempted. Also, when an interrupt occurs, the register context of the running task must be preserved in order for the operations performed during the interrupt to not corrupt the contents of the registers used by the task when it got interrupted. For the Cortex-A9, the context save contents of a blocked or pre-empted task is different from the one used in an interrupt. The following table lists the number of bytes required by each type of context save operation:

**Table 4-1 Context Save Stack Requirements**

When sizing the stack to allocate to a task, there are three factors to take in account. The first factor is simply that every task in the application needs at least the area to preserve the task context when it is preempted or blocked. Second, add to all this the stack required by the code implementing the task operation, or the interrupt operation.

NOTE: The ARM Cortex-A9 processor needs alignment on 8 byes for some instructions accessing memory. When stack memory is allocated, mAbassi guarantees the alignment. This said, when sizing OS\_STATIC\_STACK or OS\_ALLOC\_SIZE, make sure to take in account that all allocation performed through these memory pools are by block size multiple of 8 bytes.

# 5 Memory Configuration

The mAbassi kernel is not a kernel entered though a service request, such as the SWI on the Cortex-A9. The kernel is a regular function, protected against re-entrance or multiple core entrance. The kernel code executes as part of the application code, with the same processor mode and access privileges.

## 6 Search Set-up

The search results are identical to the single core Cortex-A9 port as Abassi and mAbassi use the same code for the search algorithm. Please refer to the single core Cortex-A9 port document [R2] for the measurements.

Rev 1.9 Page 31

### 7 API

The ARM Cortex-A9 supports multiple types of exceptions. Defaults exception handlers are supplied with the distribution code, but each one of them can be overloaded by an application specific function. The default handlers are simply an infinite loop (except FIQ, which is a do-nothing with return from exception). The choice of an infinite loop was made as this allows full debugging, as all registers are left untouched by the defaults handlers. The following sub-sections describe each one of the default exception handlers.

#### 7.1 DATAabort\_Handler

#### **Synopsis**

```

#include "mAbassi.h"

void DATAabort_Handler(void);

```

#### **Description**

DATAabort\_Handler() is the exception handler for a data abort fault. In the distribution code, this is implemented as an infinite loop. If the application needs to perform special processing when a data fault occurs, all there is to do is to include a function with the above function prototype, and it will overload the supplied data abort handler. As this is an exception, the return must be performed with a "subs pc, lr, #8".

#### **Availability**

Always.

#### **Arguments**

void

#### Returns

void

#### Component type

Function

#### **Options**

#### Notes

This is an exception function, executing in the abort processor mode. This means the abort stack is in use instead of the user stack, and the IRQ interrupts are disabled.

#### See also

```

FIQ_Handler() (Section 7.2)

PFabort_Handler() (Section 7.3)

SWI_Handler() (Section 7.4)

Undef_Handler() (Section 7.5)

```

#### 7.2 FIQ\_Handler

#### **Synopsis**

```

#include "mAbassi.h"

void FIQ_Handler(void);

```

#### **Description**

FIQ\_Handler() is the handler for a fast interrupt request. In the distribution code, this is implemented as a return only. If the application needs to handle fast interrupts, all there is to do is to include a function with the above function prototype and it will overload the supplied fast interrupt handler. As this is an exception, the return must be performed with a "subs pc, 1r, #4".

#### **Availability**

Always.

#### **Arguments**

void

#### Returns

void

#### Component type

Function

#### **Options**

#### Notes

This is an exception function, executing in the FIQ processor mode. This means the FIQ stack is in use instead of the user stack, and the FIQ are now disabled and IRQ interrupts are also disabled.

#### See also

```

DATAabort_Handler() (Section 7.1)

PFabort_Handler() (Section 7.3)

SWI_Handler() (Section 7.4)

Undef_Handler() (Section 7.5)

```

#### 7.3 PFabort\_Handler

#### **Synopsis**

```

#include "mAbassi.h"

void PFabort_Handler(void);

```

#### **Description**

PFabort\_Handler() is the exception handler for a pre-fetch abort fault. In the distribution code, this is implemented as an infinite loop. If the application needs to perform special processing when a pre-fetch fault occurs, all there is to do is to include a function with the above function prototype and it will overload the supplied data abort handler. As this is an exception, the return must be performed with a "subs pc, lr, #4".

#### **Availability**

Always.

#### **Arguments**

void

#### Returns

void

#### Component type

Function

#### **Options**

#### Notes

This is an exception function, executing in the abort processor mode. This means the abort stack is in use instead of the user stack, and the IRQ interrupts are disabled.

#### See also

```

DATAabort_Handler() (Section 7.1)

FIQ_Handler() (Section 7.2)

SWI_Handler() (Section 7.4)

Undef_Handler() (Section 7.5)

```

#### 7.4 SWI\_Handler

#### **Synopsis**

```

#include "mAbassi.h"

void SWI Handler(int SWInmb);

```

#### Description

SWI\_Handler() is the exception handler for software interrupts that are not handled or reserved by mAbassi. The number of the software interrupt is passed through the function argument SWInmb. This is a regular function; do not use the exception instruction "movs pc, 1r".

#### **Availability**

Always.

#### **Arguments**

SWInmb

Number of the software interrupt. The interrupt numbers 0 to 7 must not be used by the application as they are used / reserved by the RTOS.

#### Returns

void

#### Component type

Function

#### **Options**

#### Notes

This is a regular function, but executing in the supervisor processor mode. This means the supervisor stack is in use instead of the user stack, and the IRQ interrupts are disabled.

#### See also

```

DATAabort_Handler() (Section 7.1)

FIQ_Handler() (Section 7.2)

FPabort_Handler() (Section 7.3)

Undef_Handler() (Section 7.5)

```

## 7.5 Undef\_Handler

#### **Synopsis**

```

#include "mAbassi.h"

void Undef_Handler(void);

```

#### **Description**

Undef\_Handler() is the exception handler for a undefined instruction fault. In the distribution code, this is implemented as an infinite loop. If the application needs to perform special processing when an undefined instruction fault occurs, all there is to do is to include a function with the above function prototype, and it will overload the supplied undefined instruction abort handler. As this is an exception, the return must be performed with a "movs pc, 1r".

## Availability

Always.

#### Arguments

void

#### Returns

void

#### Component type

Function

#### **Options**

#### Notes

This is an exception function, executing in the abort processor mode. This means the abort stack is in use instead of the user stack, and the IRQ interrupts are disabled.

#### See also

```

DATAabort_Handler() (Section 7.1)

FIQ_Handler() (Section 7.2)

PFabort_Handler() (Section 7.3)

SWI_Handler() (Section 7.4)

```

# 8 Chip Support

No custom chip support is provided with the distribution because most device manufacturers provide a BSP, i.e. code to configure the peripherals on their devices. The distribution code contains some of the manufacturer's open source libraries.

Basic support for the Generic Interrupt Controller (GIC) is provided in this port as SMP/BMP multi-core on the Cortex-A9 MPCore device requires the use of interrupts. The following sub-sections describe the two support components.

#### 8.1 GICenable

#### **Synopsis**

```

#include "mAbassi.h"

void GICenable(int IntNmb, int Prio, int Edge);

```

#### **Description**

GICenable() is the component used to enable an interrupt number (called IDnn in the literature) on the Generic Interrupt Controller (GIC). The interrupt configuration is always applied to the core on which GICenable() is executing.

#### **Availability**

Always.

#### Arguments

IntNmb Interrupt number to enable

Prio Priority of the interrupt

0 : highest priority

255 : lowest priority

Edge or level detection

== 0 : level detection != 0 : edge detection

#### Returns

void

Edge

#### Component type

Function

#### **Options**

#### Notes

On the Cortex-A9 MPCore, some GIC registers are local to the core, while others are global across all cores. Care must be taken when using GICenable().

When the interrupt number (argument IntNmb) is non-negative, then the GIC is programmed to target the interrupt to the core it's currently operating on. If the interrupt number is negative, then the interrupt number —IntNmb is targeted to all cores.

The function GICenable() is implemented in assembly language, in the file mabassi\_SMP\_CORTEXA9\_GCC.s as it avoids supplying 2 port files in the distribution. If the supplied functionality does not fulfill the application needs, GICenable() can be overloaded by adding a new GICenable() function in the application. As the supplied assembly function is declared weak, it will not be included during the link process. The equivalent "C" code of the distribution implementation is supplied in comments in the assembly file.

#### See also

GICinit() (Section 8.2)

#### 8.2 GICinit

#### **Synopsis**

```

#include "mAbassi.h"

void GICinit(void);

```

## Description

GICinit() is the component used to initialize the Generic Interrupt Controller (GIC) for the needs of mAbassi. It must be used after using the OSstart() component and before GICenable() and / or OSeint() components. Also, it must be used in every COREstartN() function.

Consult the mAbassi User guide for more information on this topic [R1].

#### **Availability**

Always.

#### Arguments

void

#### Returns

void

## Component type

Function

## **Options**

#### Notes

The function <code>GICinit()</code> is implemented in assembly language, in the file <code>mAbassi\_SMP\_CORTEXA9\_GCC.s</code> as it avoids supplying 2 port files in the distribution. If the supplied functionality does not fulfill the application needs, <code>GICinit()</code> can be overloaded by adding a new <code>GICinit()</code> function in the application. As the supplied assembly function is declared weak, it will not be included during the link process. The equivalent "C" code of the distribution implementation is supplied in comments in the assembly file.

#### See also

GICenable() (Section 8.1)

## 9 Measurements

This section provides an overview of the memory requirements encountered when the RTOS is used on the Arm9 and compiled with Mentor's Code Sourcery tool chain. Latency measurements are provided, but one should remember CPU latency latencies are highly dependent on 3 factors. It first depends on how many cores are used; it also depends on the type of load balancing, i.e. if mAbassi is configured in SMP or BMP, and if the load balancing algorithm is the True or the Packed one. All these possible configurations are one part of the complexity. A second part of the complexity is where the task switch was detected and on which core(s) the task switch will occur due to that change of state. Finally, the third factor is if a core is already executing in the kernel when another needs to enter the kernel. Any combination of these dynamic factors affects differently the CPU latency of mAbassi. The specific configuration and run-time conditions are described in the latency subsection (Section 9.2)

## 9.1 Memory

The memory numbers are supplied for the two limit cases of build options (and some in-between): the smallest footprint is the RTOS built with only the minimal feature set, and the other with almost all the features. For both cases, names are not part of the build. This feature was removed from the metrics because it is highly probable that shipping products utilizing this RTOS will not include the naming of descriptors, as its usefulness is mainly limited to debugging and making the opening/creation of components runtime safe.

The code size numbers are expressed with "less than" as they have been rounded up to multiples of 25 for the "C" code. These numbers were obtained using the release version 1.34.36 of the RTOS and may change in other versions. One should interpret these numbers as the "very likely" numbers for other released versions of the RTOS.

The code memory required by the RTOS includes the "C" code and assembly language code used by the RTOS. The code optimization settings of the compiler that were used for the memory measurements are:

1. Debugging model: Off<sup>3</sup> (option –g not specified)

2. Optimization level: -os

Target -arch=armv7-a -mtune=cortex-a9 -mcpu=cortex-a9

4. FPU -mfloat-abi-soft

<sup>&</sup>lt;sup>3</sup> Debugging is turned off as it restricts the optimizer.

Table 9-1 "C" Code Memory Usage

| Description                                         | Thumb Size   | 32-Bit Size  |

|-----------------------------------------------------|--------------|--------------|

| Minimal Build                                       | < 1425 bytes | < 2175 bytes |

| + Runtime service creation / static memory          | < 1650 bytes | < 2475 bytes |

| + Runtime priority change                           | < 1675 bytes | < 2475 bytes |

| + Mutex priority inheritance                        |              |              |

| + FCFS                                              |              |              |

| + Task suspension                                   |              |              |

| + Timer & timeout                                   | < 2175 bytes | < 3225 bytes |

| + Timer call back                                   |              |              |

| + Round robin                                       |              |              |

| + Events                                            | < 3000 bytes | < 4425 bytes |

| + Mailbox                                           |              |              |

| Full Feature Build (no names)                       | < 3600 bytes | < 5500 bytes |

| Full Feature Build (no name / no runtime creation)  | < 3775 bytes | < 6550 bytes |

| Full Feature Build (no names / no runtime creation) | < 4275 bytes | < 6050 bytes |

| + Timer services module                             |              |              |

| OS_NEWLIB_REENT > 0                                 | n/a          | +1048 bytes  |

| OS_NEWLIB_REENT < 0                                 | n/a          | +304 bytes   |

| True SMP (OS_MP_TYPE == 2)                          | +0 bytes     | +0 bytes     |

| Packed SMP (OS_MP_TYPE == 3)                        | ~ +100 bytes | ~ +100 bytes |

| True BMP (OS_MP_TYPE == 4)                          | ~ +300 bytes | ~ +400 bytes |

| Packed BMP (OS_MP_TYPE == 5)                        | ~ +350 bytes | ~ +475 bytes |

The selection of load balancing type affects the "C" code size. The added memory requirements are indicated as approximate because depending on the build option combination, the kernel code is different. As such, the optimizer does not deliver the same code size.

Table 9-2 Assembly Code Memory Usage

| Description                                   | Size |       |

|-----------------------------------------------|------|-------|

| Assembly code size (non-privilege / >1 core)  | 1308 | bytes |

| Assembly code size (non-privilege / ==1 core) | 788  | bytes |

| Assembly code size (privilege / >1 core)      | 1040 | bytes |

| Assembly code size (privilege / ==1 core)     | 656  | bytes |

| VFPv3                                         | +116 | bytes |

| VFPv3D16                                      | +108 | bytes |

| Saturation Bit Enabled                        | +36  | bytes |

| GICinit() (>1 core)                           | +144 | bytes |

| GICinit() (=1 core)                           | +84  | bytes |

| GICenable() (>1 core)                         | +276 | bytes |

| GICenable() (=1 core)                         | +276 | bytes |

| OS_NEWLIB_REENT > 0                           | +84  | bytes |

| OS_NEWLIB_REENT < 0                           |      | bytes |

| Altera Cyclone V Support                      |      | bytes |

| TI OMAP 4460 Support                          | +16  | bytes |

| Xilinx Zynq Support                           | +84  | bytes |

There are two aspects when describing the data memory usage by the RTOS. First, the RTOS needs its own data memory to operate, and second, most of the services offered by the RTOS require data memory for each instance of the service. As the build options affect either the kernel memory needs or the service descriptors (or both), an interactive calculator has been made available on the Code Time Technologies website.

## 9.2 Latency